MOS 管被击穿从来不是单一“电压太高”这么简单,而是“电压、电流、能量、速度、温度”五环中任何一环掉链子,都会把芯片瞬间推到硅本征激发区。下面把现场最常见的七种击穿机理拆开讲,并给出每个机理对应的“现场脚印”,方便研发工程师在失效分析时快速定位真凶。

一、电压型击穿:把电场直接怼进硅里

漏源雪崩击穿(Avalanche)机理:VDS 超过 BV DSS,漏端耗尽层电场 > 3×10⁵ V/cm,电子-空穴对雪崩倍增,电流雪崩式上升。脚印:芯片表面出现“熔洞”或“铝迁移树”,但位置随机,击穿能量大时整个有源区炸飞。诱因:输入浪涌、变压器漏感、电机反灌、PCB 尖峰吸收不足。

栅氧击穿(Gate Oxide Rupture)机理:VGS 超过 8~10 MV/cm(折合 20 V 栅氧只要 25 nm 厚),SiO₂ 晶格断裂,形成永久短路点。脚印:栅极与源/漏之间电阻从 10¹² Ω 跌到 <10 Ω,EMMI 可看到栅极边缘亮点。诱因:ESD 手环没戴、栅极悬空、驱动负压欠冲、测试机台漏电。

二、电流型击穿:电压没超标,但电流把硅“烧穿”3. 体二极管反向恢复击穿(dv/dt Induced Turn-on)机理:二极管关断时 Qrr 被瞬间抽走,产生 5~20 A 的反向恢复尖峰,电流密度 > 3×10⁵ A/cm²,局部热点 > 600 °C,硅熔成球。脚印:失效点总在体二极管拐角,SEM 下可见“硅熔球”与铝层吹孔。诱因:H 桥/LLC 死区太小、同步整流管换流过快、并联器件电流不均。

雪崩能量过载(Single Pulse E AS > Rated)机理:雪崩电压虽未到极限,但单次能量 ½×L×I² 超过芯片可吸收值,结温 > 400 °C,铝-硅共熔。脚印:焊线根部熔断,塑封壳鼓包,X 光可见“金属球”回流。诱因:电机堵转、继电器掉线、输出短路保护延迟。

三、热型击穿:温度先超标,电压再“补刀”5. 热失控二次击穿(Thermal Runaway)机理:R DS(on) 正温度系数→热点电流更集中→温度再升,形成正反馈,最终局部 > 600 °C,硅-铝共熔。脚印:热点呈“彗星尾”状,从焊线脚延伸到芯片中央,红外热像仪可复现。诱因:散热片没贴平、风道被堵、导热硅脂干裂、并联不均流。

重复雪崩疲劳(Repetitive E AR 超限)机理:每次雪崩注入少量载流子,界面陷阱电荷积累,BV DSS 逐次降低 2~5 %,最终在额定电压下击穿。脚印:击穿电压比规格书低 10~30 V,但芯片表面无熔洞,属“软失效”。诱因:PFC 连续升压、DCM 反激每周期都进雪崩、LED 驱动电感值太小。

四、场-热-电流耦合型:高频高压“组合拳”7. 米勒平台误导通 + 二次击穿机理:高 dv/dt 通过 C rss 耦合到栅极,栅压被抬到 2~4 V,MOS 瞬间进入线性区,V DS × I D 功耗 10×于正常开关,局部结温 > 400 °C,硅熔穿。脚印:失效位置在栅极总线末端,栅氧化层完整但漏源已短路,EMMI 热点沿沟道呈“线状”。诱因:栅极驱动阻抗过高、负压关断不足、PCB 共源电感太大、没有米勒钳位。

五、设计 checklist:把击穿拦在实验室

电压:硬开关拓扑按 1.5×V in(max) 选 BV DSS,并测 100 MHz 示波器尖峰;

电流:核算 ½×L×I² 是否 < 0.8×E AS(@T j(max)),电机负载必须测堵转;

栅极:驱动环路面积 < 1 cm²,负压关断 ≤−3 V,加 4.7 kΩ 栅-源下拉;

热阻:R θJA 实测 < 规格书 80 %,风道 45 °C 环温满载 2 h 结温 < 125 °C;

雪崩:重复工况用“雪崩优化”工艺(OptiMOS 5/6、Trench 6),普通 MOS 禁止每周期雪崩;

dv/dt:测 V DS 上升沿 < 50 V/ns 时栅极无抬升,否则加米勒钳位或降低驱动电阻;

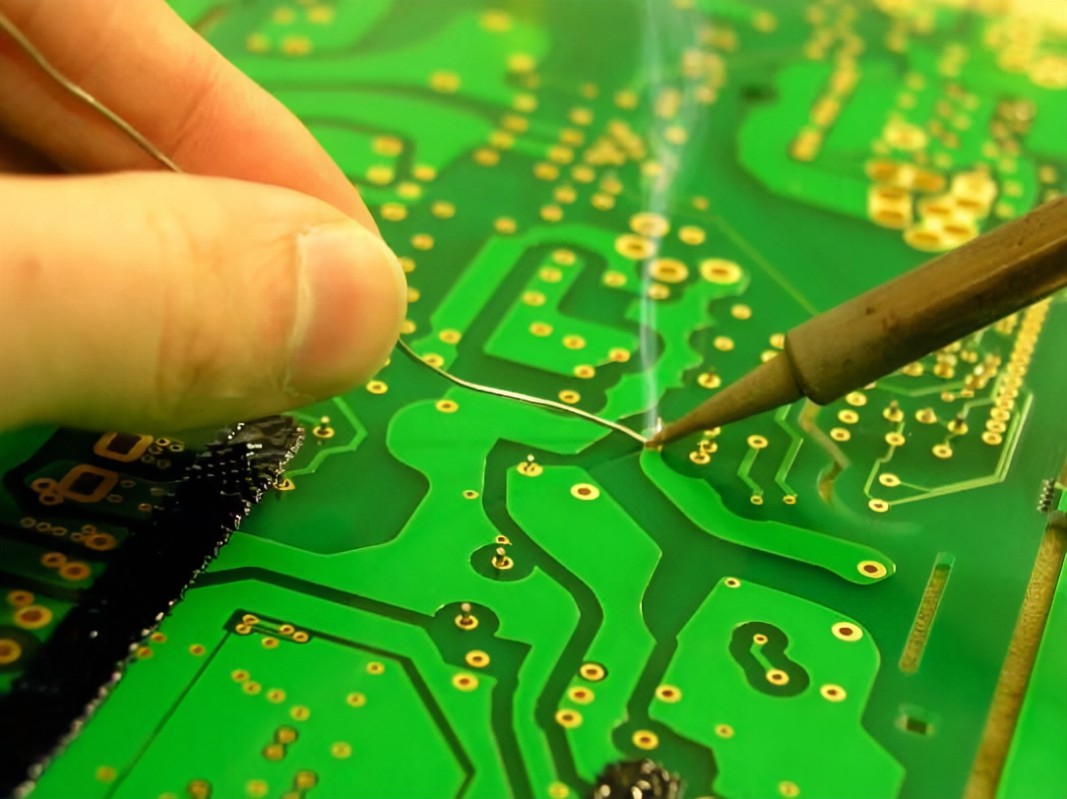

ESD:栅极引脚加 15 V TVS,手工焊接戴接地手环,测试机台漏电流 < 1 µA。

一句话总结MOS 管击穿=“电场击穿硅”或“电流烧化铝”或“温度先失控”,而现场 80 % 的失效都是“看起来电压没超,其实能量/温度/速度早已破表”。把雪崩能量、dv/dt、热阻三条线守死,就能把击穿概率从千分之几拉到百万分之几。